### CPE201 Digital Design

By Benjamin Haas

Class 18: Flip-Flops

### Vocabulary

- Bistable Multivibrator

- 2 States

- Synchronous

- There is a clock

- Clock

- Signal that alternates H/L at a set interval

#### Vocab

- Edge Triggered

- State changes on edg

- Positive or rising edge

Negative or falling ed

D

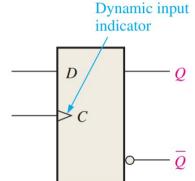

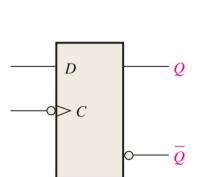

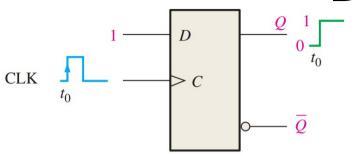

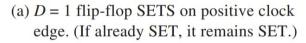

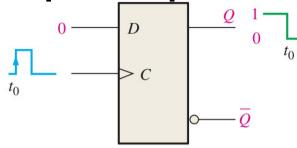

### D Flip-Flop

(b) *D* = 0 flip-flop RESETS on positive clock edge. (If already RESET, it remains RESET.)

Truth table for a positive edge-triggered D flip-flop.

| Inputs |        | Outputs                |                               |              |

|--------|--------|------------------------|-------------------------------|--------------|

| D      | CLK    | $\boldsymbol{\varrho}$ | $\overline{oldsymbol{arrho}}$ | Comments     |

| 0      | ↑<br>↑ | 0                      | 1<br>0                        | RESET<br>SET |

↑ = clock transition LOW to HIGH

# Example

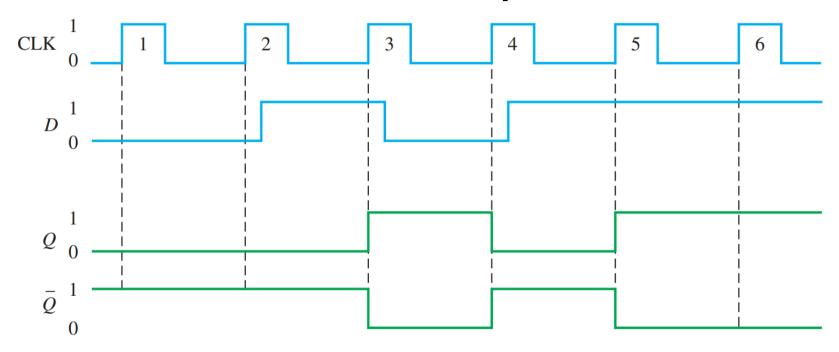

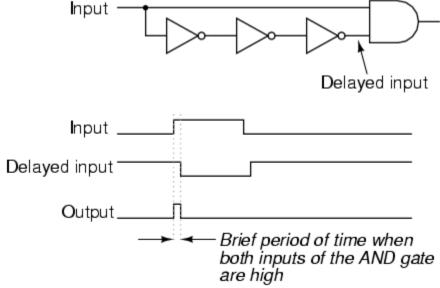

### **Edge Detection**

Output

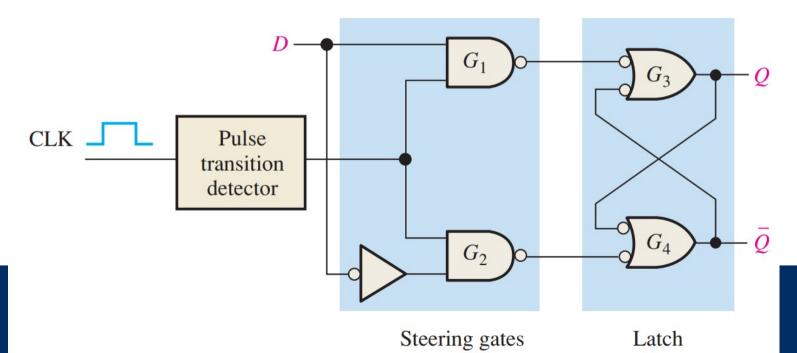

#### Circuit

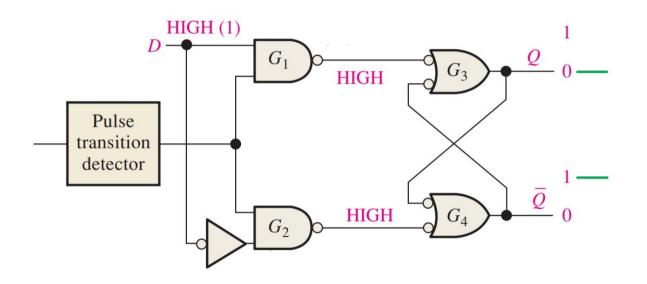

G<sub>3</sub> and G<sub>4</sub> are NANDs (like from latches)

### Circuit Walkthrough

Truth table for a 2-input NAND gate.

| Inp              | outs | Output |  |  |

|------------------|------|--------|--|--|

| $\boldsymbol{A}$ | В    | X      |  |  |

| 0                | 0    | 1      |  |  |

| 0                | 1    | 1      |  |  |

| 1                | 0    | 1      |  |  |

| 1                | 1    | 0      |  |  |

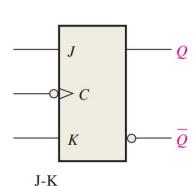

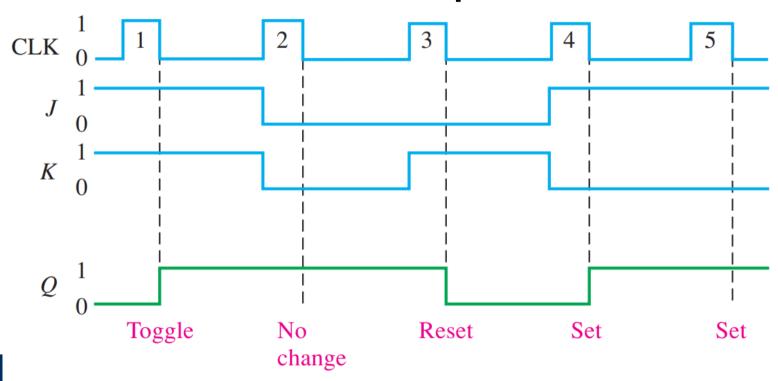

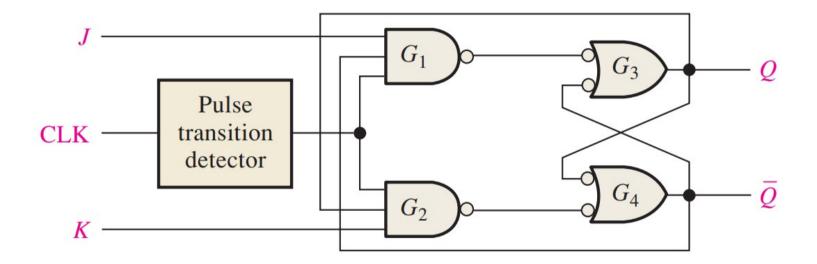

# J-K Flip-Flop

• S-R Latch+

Truth table for a positive edge-triggered J-K flip-flop

| Inputs |   |          | Outputs          |                          |           |

|--------|---|----------|------------------|--------------------------|-----------|

| J      | K | CLK      | Q                | $\overline{\mathcal{Q}}$ | Comments  |

| 0      | 0 | 1        | $Q_0$            | $\overline{Q}_0$         | No change |

| 0      | 1 | 1        | 0                | 1                        | RESET     |

| 1      | 0 | <b>1</b> | 1                | 0                        | SET       |

| 1      | 1 | 1        | $\overline{Q}_0$ | $Q_0$                    | Toggle    |

$\uparrow = \text{clock transition LOW to HIGH}$   $Q_0 = \text{output level prior to clock transition}$

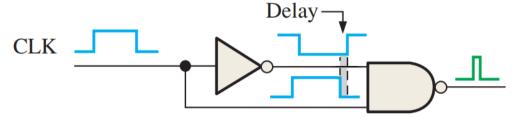

# Example

#### Circuit

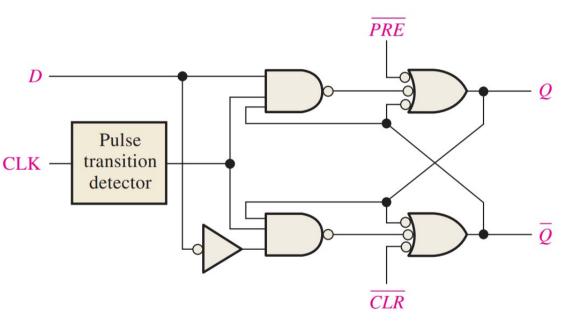

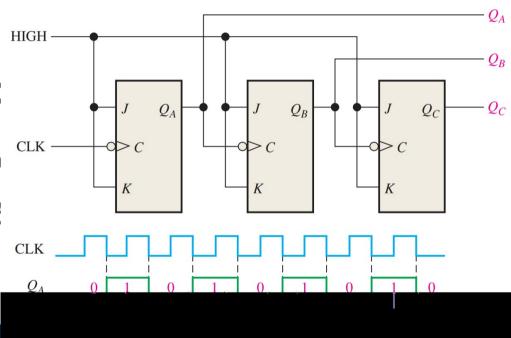

### Asynchronous Set and Reset

- Independent on clock

- Initialization on startup

- Override

- Also called Preset and Clear

### Circuit

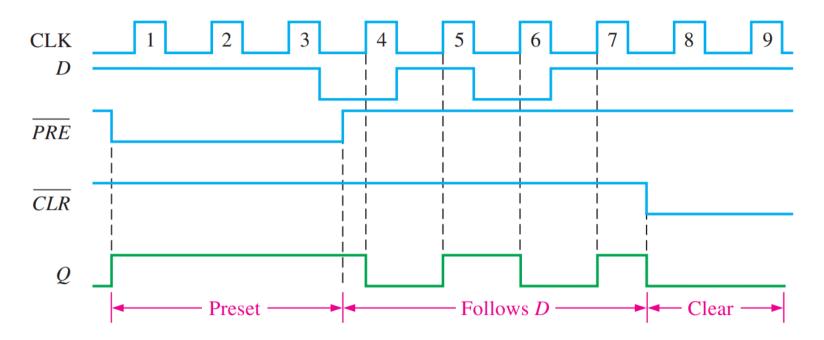

#### Preset and Clear

- Reaches into the Latch portion of the circuit

- Can also be done in J-K Flip-Flop

- Active Low inputs

- Normal operation is both high

- Both low creates latch invalid state

# Example

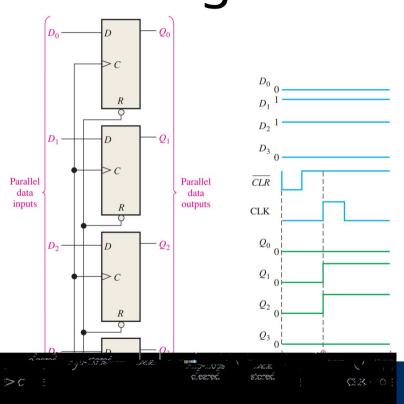

# Application – Data Storage

- Parallel storage

- Data on lines stored at each clock

- Covered more later

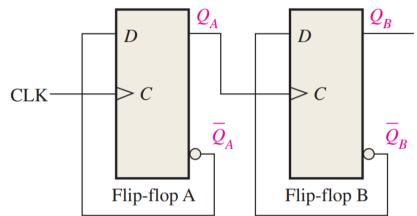

### Application - Frequency Division

- Divide by 2

- Good for running multiple subsystems

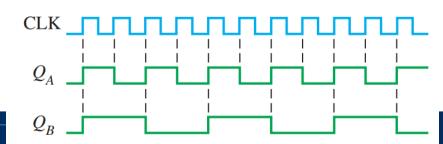

### **Application - Counting**

- Like freq division

- Line up the divisic to count in binary CLK

- Counts clock cycle

- J-Ks instead of Ds

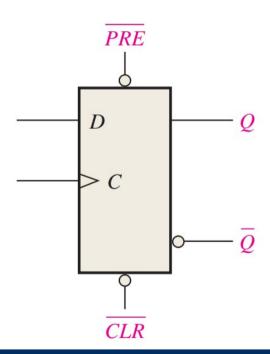

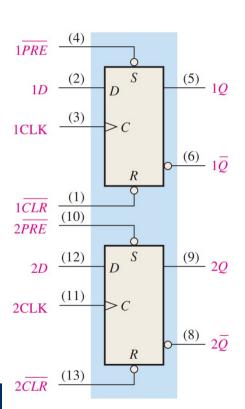

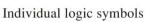

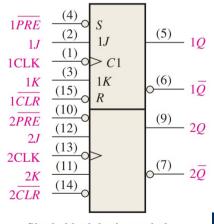

# Real Chips - 74HC74 and

Single block logic symbol Note: The S and R inside the block indicate that  $\overline{PRE}$ SETS and  $\overline{CLR}$  RESETS.

Individual logic symbols

Single block logic symbol

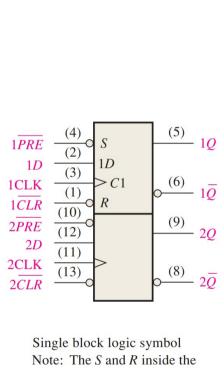

The 74HC112 dual negative edge-triggered J-K flip-flop.

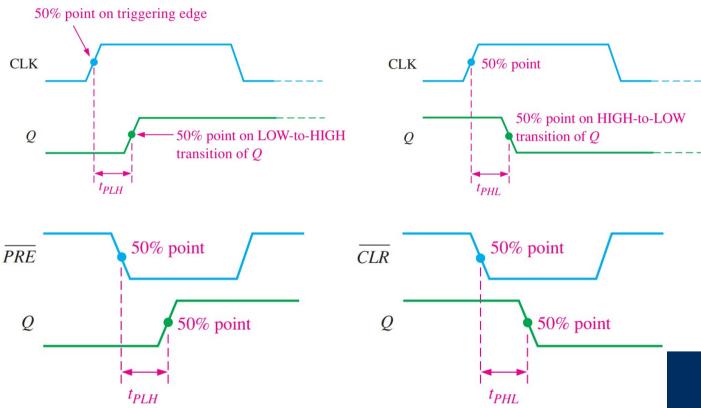

# Propagation Delays

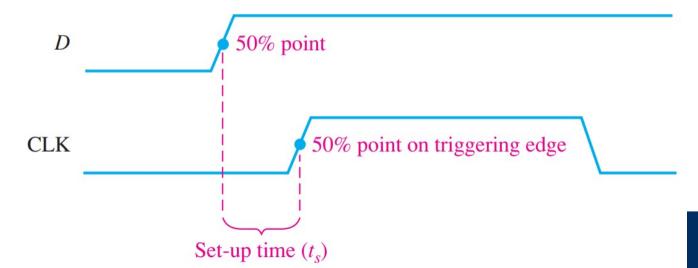

### Setup Time

Data time on the line BEFORE clocking it in

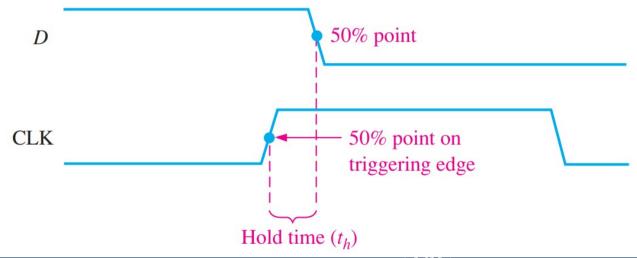

#### **Hold Time**

Data time on the line AFTER clocking it in

# Reading

- This lecture

- Sections 7.2-7.4

- Next lecture

- Sections 7.5-7.7